# **10. IC SPEC**

## DVI

# Consumer Component Interfaces

#### DigitalVisual Interface (DVI)

DVI was developed for transferring uncompressed digital video from a computer to a display monitor. It may also be used for interfacing devices such as settop boxes to televisions. DVI enhances the Digital Flat Panel (DFP) Interface by supporting more formats and timings, and supporting the Highbandwidth Digital Content Protection (HDCP) specification to ensure unauthorized copying of material is prevented. The interface supports VESA's Extended Display Identification Data (EDID) standard, Display Data Channel (DDC) standard, and Monitor Timing Specification (DMT). DDC and EDID enable automatic display detection and configuration. "TFT data mapping" is supported as the minimum requirement: one pixel per clock, eight bits per channel, MSB justified.

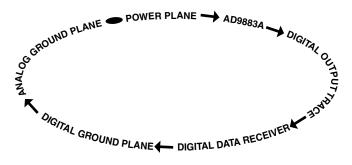

DVI uses transition-minimized differential signaling (TMDS). Eight bits of video data are converted to a 10-bit transition-minimized, DCbalanced value, which is then serialized. The receiver deserializes the data, and converts it back to eight bits. Thus, to transfer digital R'G'B' or YCbCr data requires three TMDS signals that comprise one TMDS link.

To further enhance DVI for the consumer market, Silicon Image developed a method of transferring digital audio over the existing clock channel.

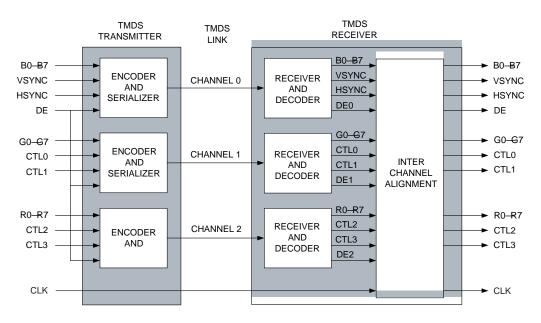

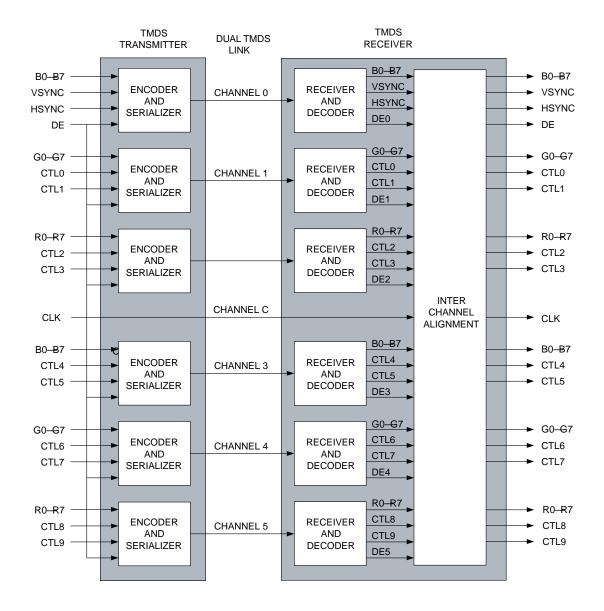

#### **TMDS** Links

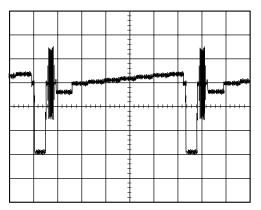

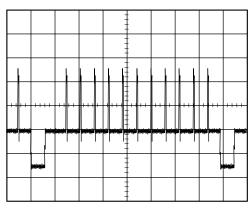

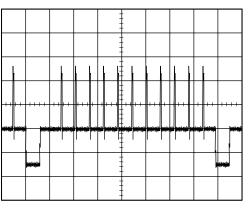

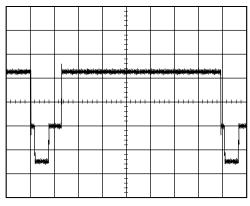

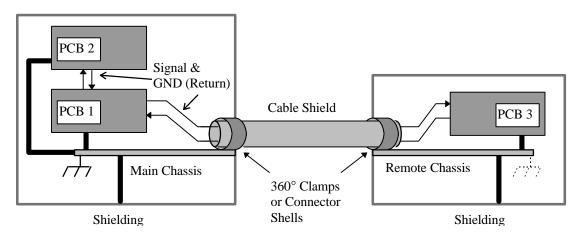

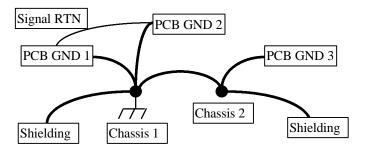

Either one or two TMDS links may be used, as shown in Figures 1. and 2. depending on the formats and timing required. A system supporting two TMDS links must be able to switch dynamically between formats requiring a single link and formats requiring a dual link.

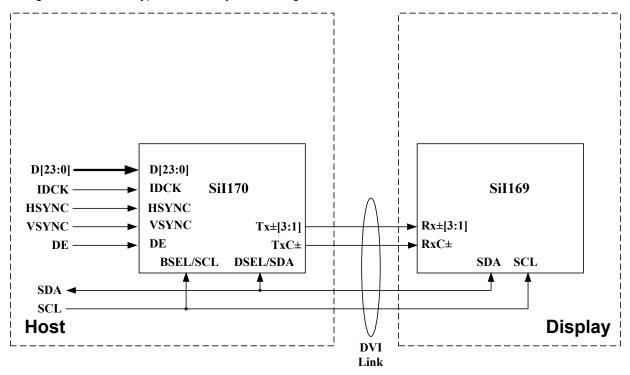

Figure1. DVI Single TMDS Link.

Figure 2. DVI Dual TMDS Link.

A single TMDS link is used to support all formats and timings requiring a clock rate of 25-165 MHz. Formats and timings requiring a clock rate >165 MHz are implemented using two TMDS links, with each TMDS link operating at one-half the frequency. Thus, the two TMDS links share the same clock and the bandwidth is shared evenly between the two links.

#### Video Data Formats

Typically, 24-bit R'G'B' data is transferred over a link, although any data format may be used, including 24-bit YCbCr for consumer applications. For applications requiring more than eight bits per color component, the second TMDS link may be used for the additional least significant bits.

#### **Control Signals**

In addition to the video data, there are up to 14 control signals:

| HSYNC     | horizontal sync   |

|-----------|-------------------|

| VSYNC     | vertical sync     |

| DE        | data enable       |

| CTL0-CTL3 | reserved (link 0) |

| CTL4-CTL9 | reserved (link 1) |

| CLK       | 1x sample clock   |

| 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  |  |

|----|----|----|----|----|----|----|----|--|

| 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |  |

| 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 |  |

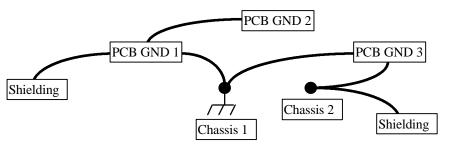

Figure 3. DVI Digital-Only Connector.

While DE is a "1," active video is processed. While DE is a "0," the HSYNC, VSYNC and CTL0-CTL9 signals are processed. HSYNC and VSYNC may be either polarity.

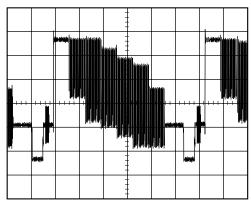

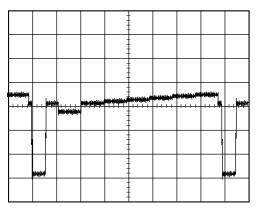

#### Digital-Only Connector

The digital-only connector, which supports dual link operation, contains 24 contacts arranged as three rows of eight contacts, as shown in Figure 3. Table 5. lists the pin assignments.

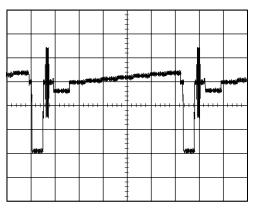

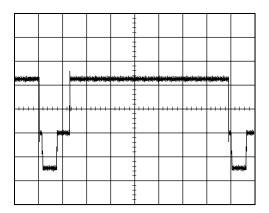

#### **Digital-Analog Connector**

In addition to the 24 contacts used by the digital-only connector, the 29-contact digital-analog connector contains five additional contacts to support analog video as shown in Figure 4. Table 6. lists the pin assignments.

| HSYNC | horizontal sync    |

|-------|--------------------|

| VSYNC | vertical sync      |

| RED   | analog red video   |

| GREEN | analog green video |

| BLUE  | analog blue video  |

The operation of the analog signals is the same as for a standard VGA connector.

| $\left[ \right]$ | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  |  |

|------------------|----|----|----|----|----|----|----|----|--|

|                  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |  |

|                  | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 |  |

Figure 4. DVI Digital-Analog Connector.

| Pin | Signal   | Pin | Signal          | Pin | Slgnal |

|-----|----------|-----|-----------------|-----|--------|

| 1   | D2-      | 9   | D1-             | 17  | D0-    |

| 2   | D2       | 10  | D1              | 18  | D0     |

| 3   | shield   | 11  | shield          | 19  | shield |

| 4   | D4-      | 12  | D3-             | 20  | D5-    |

| 5   | D4       | 13  | D3              | 21  | D5     |

| 6   | DDC SCL  | 14  | +5V             | 22  | shield |

| 7   | DDC SDA  | 15  | ground          | 23  | CLK    |

| 8   | reserved | 16  | Hot Plug Detect | 24  | CLK-   |

Table 5. DVI Digital-Only Connector Signal Assignments.

| Pin | Signal  | Pin | Signal          | Pin | Slgnal |

|-----|---------|-----|-----------------|-----|--------|

| 1   | D2-     | 9   | D1-             | 17  | D0-    |

| 2   | D2      | 10  | D1              | 18  | D0     |

| 3   | shield  | 11  | shield          | 19  | shield |

| 4   | D4-     | 12  | D3-             | 20  | D5-    |

| 5   | D4      | 13  | D3              | 21  | D5     |

| 6   | DDC SCL | 14  | +5V             | 22  | shield |

| 7   | DDC SDA | 15  | ground          | 23  | CLK    |

| 8   | VSYNC   | 16  | Hot Plug Detect | 24  | CLK-   |

| C1  | RED     | C2  | GREEN           | C3  | BLUE   |

| C4  | HSYNC   | C5  | ground          |     |        |

Table 6. DVI Digital-Analog Connector Signal Assignments.

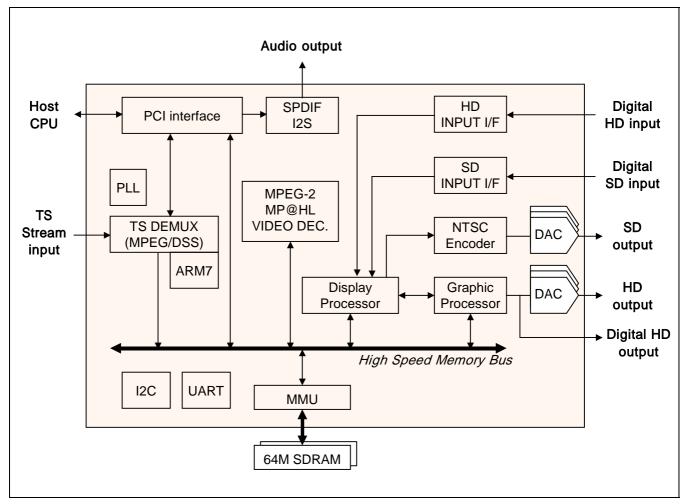

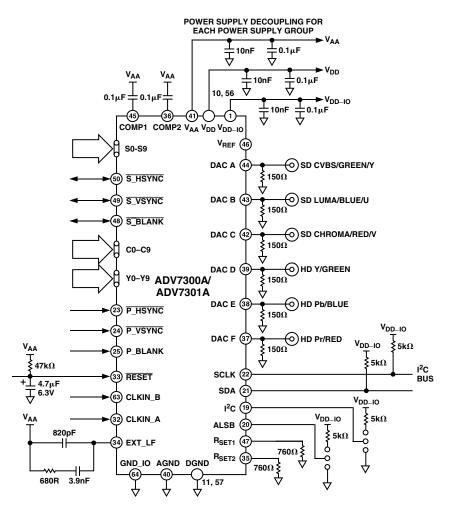

# PRODUCT OVERVIEW

## **OVERVIEW**

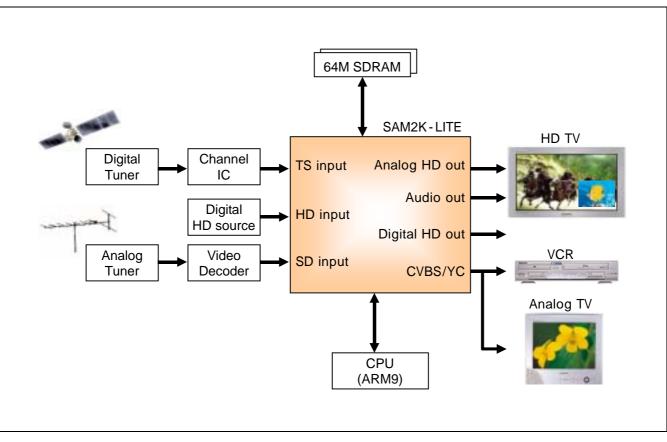

S5H2000X is an HDTV signal processing IC for digital broadcasting. It is also referred to as SAM2K-LITE.For optimum performance, SAM2K-LITE has been designed to work with built-in HDTVs or HD set-top boxes. It contains HDTV signal processing functions in a single unit and thus-allows you to easily construct a set.

This User's Manual is designed to help developers, who have a basic knowledge of MPEG and PCI, to develop STB or HDTV applications using SAM2K-LITE.

This manual contains the following topics.

- General feature

- Block diagram

- System diagram

- Pin & Control register description

- Internal module description

- TS Demux

- PCI interface

- Audio interface

- MPEG decoder

- Display processor

- Graphic processor

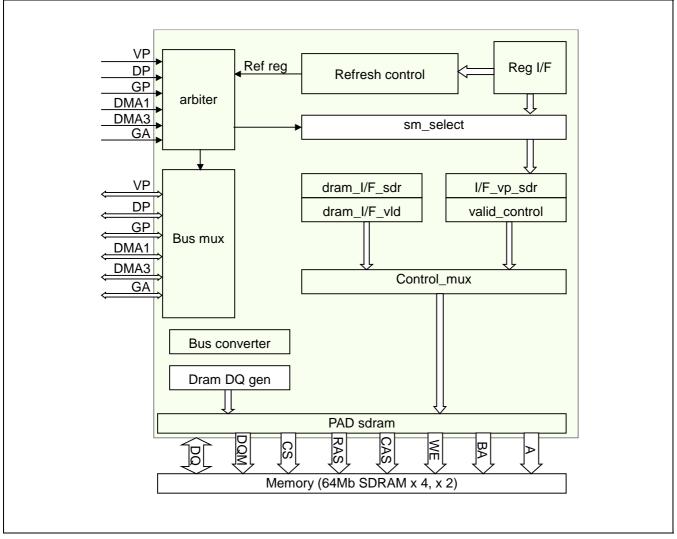

- Memory interface

- Electrical characteristics and timing spec

- PKG information

GENERAL Features

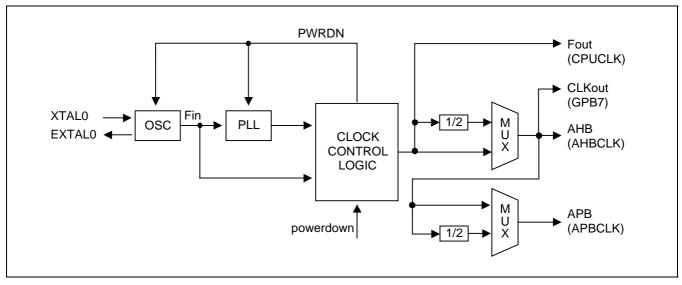

- ARM7TDMI RISC CPU

- Used for programmable TS demux

- 67.5MHz speed @ 1.8V ±0.15V

- 12Kbyte SRAM

- External memory interface

- 64bit wide SDRAM interface

- 64Mbit(32bit wide) x 4 or

64Mbit(32bit wide) x 2 SDRAM support

@ CAS latency 3

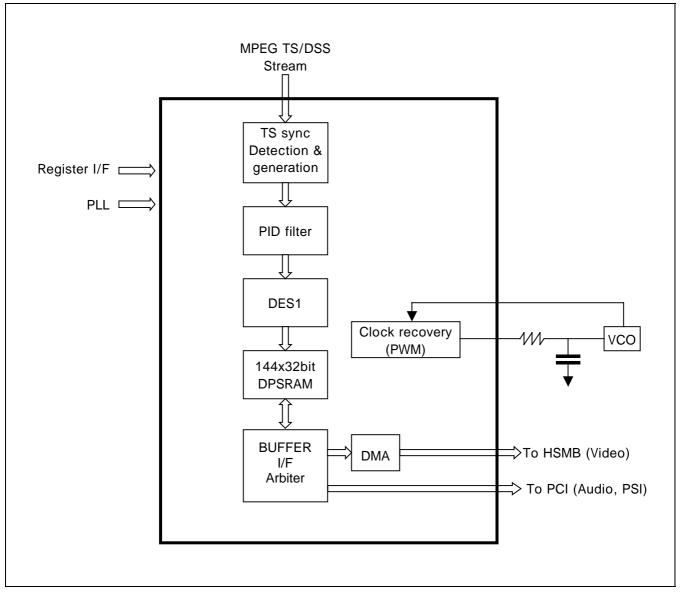

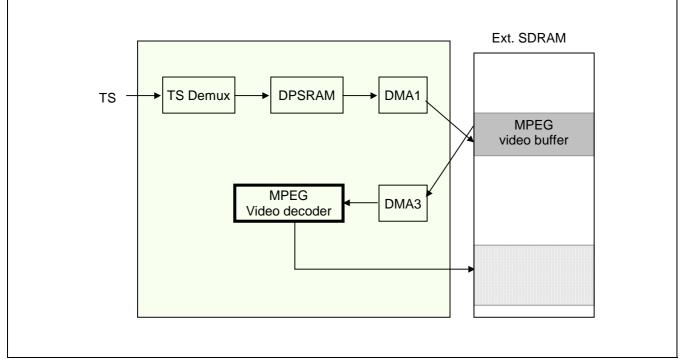

- TS (Transport Stream) Demux engine

- S/W demux architecture using ARM7TDMI

- MPEG-2 or DSS TS demux support

- DVB, ATSC support

- Built-in DES descrambler

- Up to 32 PIDs can be received at the same time

- CRC(MPEG-2 : 32bit, DSS : 16bit) support

- Video packets are transmitted to external SDRAM via DMA1.

- Audio packets are transmitted to the host CPU's memory via PCI interface.

- Allows filtering of desired information from the PSI packet and transmitting to the host CPU.

- Built-in clock recovery circuit for programmable clock recovery.

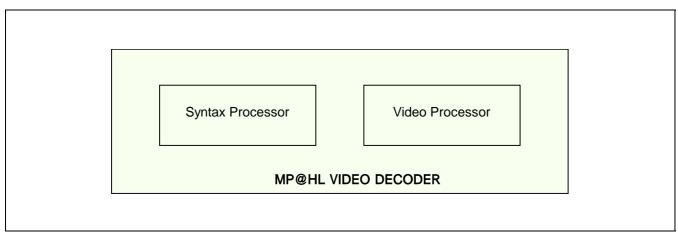

- MPEG Video decoder

- ISO/IEC 11172-2 (MPEG1) format support

- SO/IEC 13818-2 MP@HL (MPEG2) format support

- DSS MPEG1 format support

- DSS MPEG2 SD and HD format support

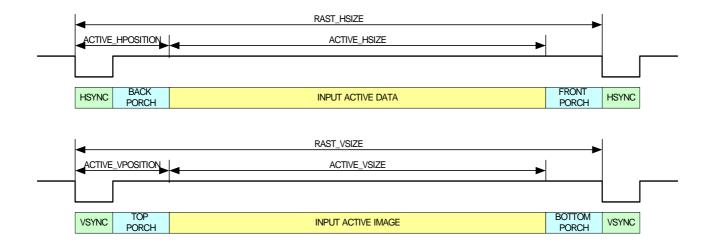

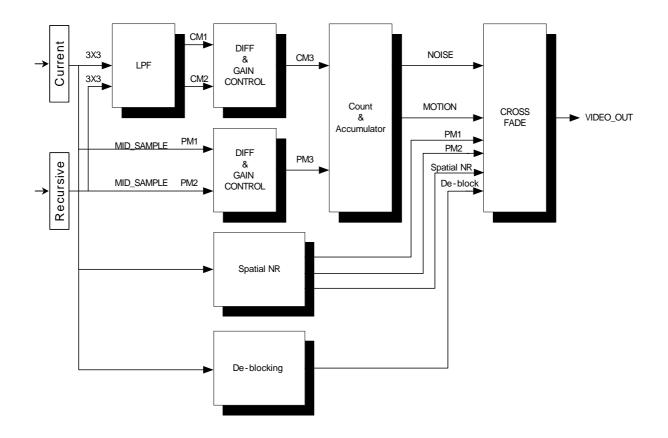

- Display processor

- 4 display planes (background, video, OSD, cursor plane)

- Letter box, pan/scan display

- Pillar-box (side well) / panorama display

- 3D IPC support

- PIP support

- Flexible color space conversion support

- Various video inputs

- TS stream input

- Digital HD (RGB) input (24bit)

- Digital SD input (8bit)

- Various video output formats

- Digital HD video output (1080i, 720p, 480p, RGB/YCbCr)

- Analog HD video output (RGB/YPbPr without sync or with 3 level sync)

- Analog SD video output (CVBS, S-video)

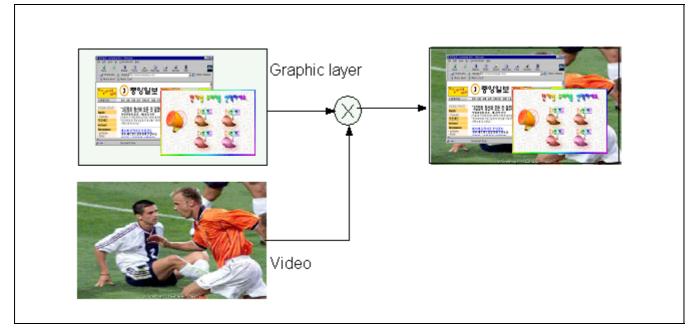

- Graphic processor

- 4 Graphic windows (on the OSD plane)

- Blending (window or pixel blending, window and pixel blending)

- H/W cursor

- 2D Graphic accelerator

- Audio input

- Audio stream or PCM input (through PCI bus)

- External PCM input

- Audio output

- IEC958 (SPDIF) audio output interface

- I2S audio output interface

- On-chip peripherals

- PCI interface (32bit, 66MHz)

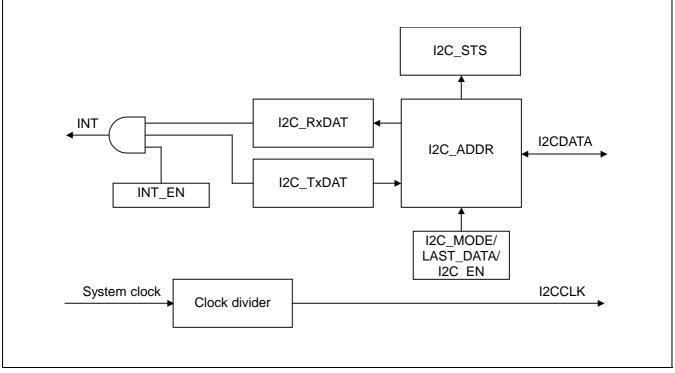

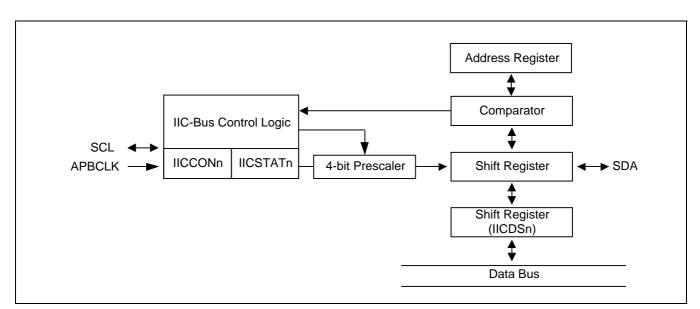

- I2C

- JTAG interface (for ARM7 only)

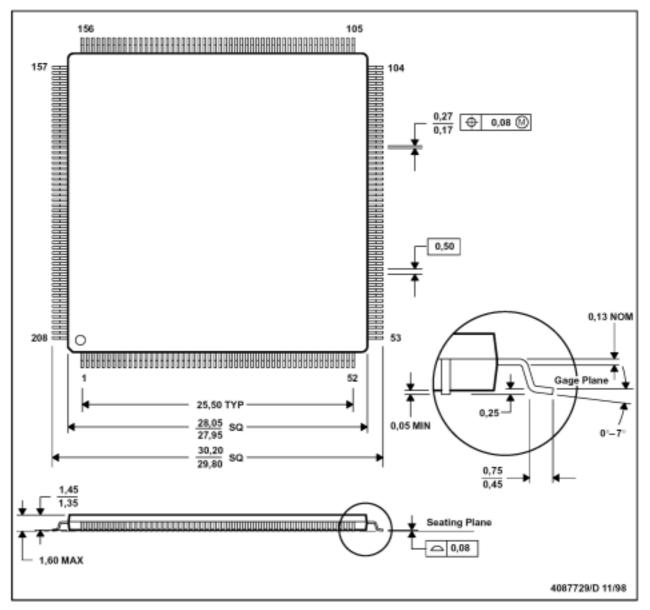

- Package

- 352 pin TBGA

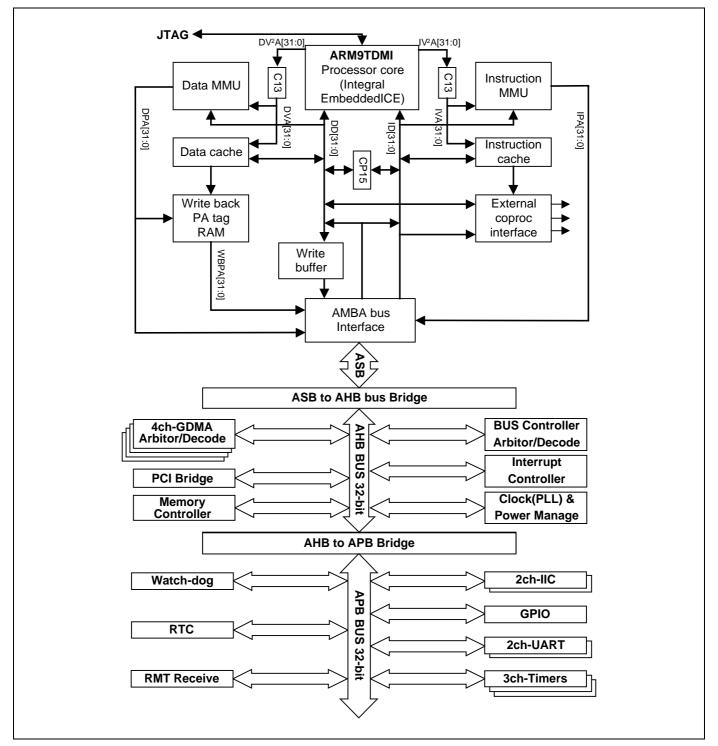

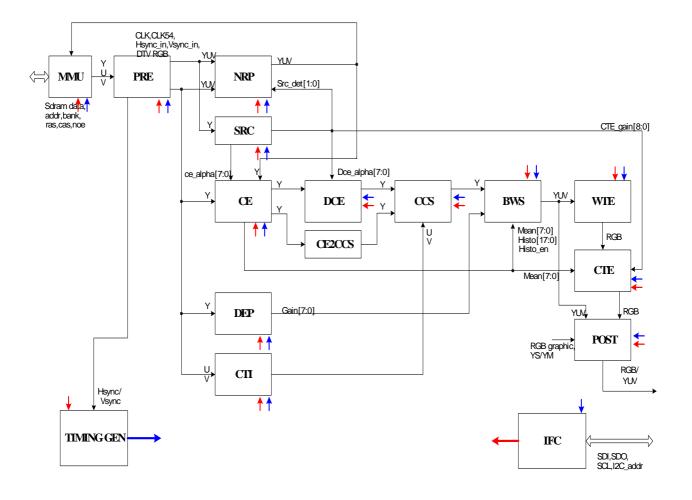

# **BLOCK DIAGRAM**

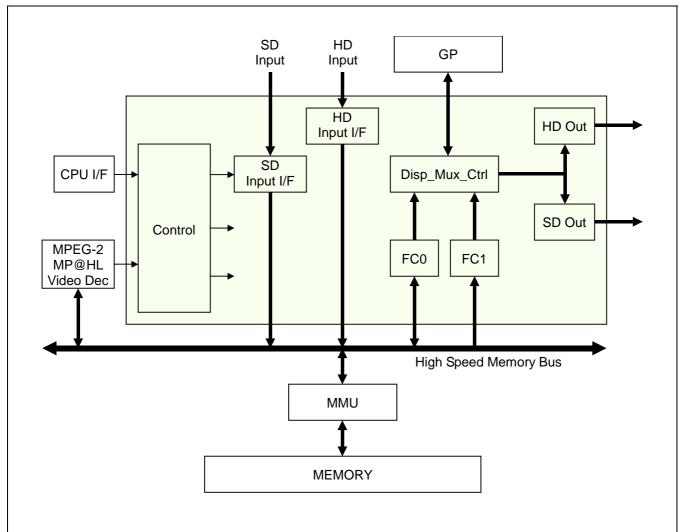

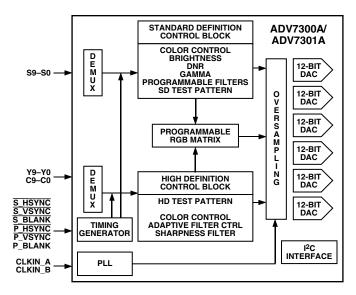

Figure 1-1. S5H2000X Block diagram

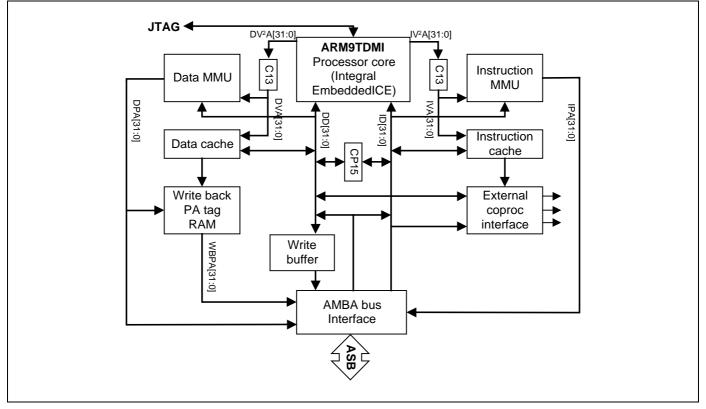

#### SYstem diagram

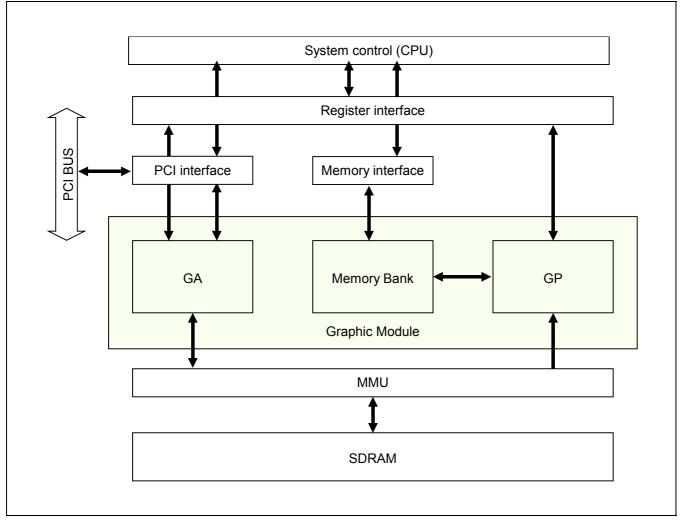

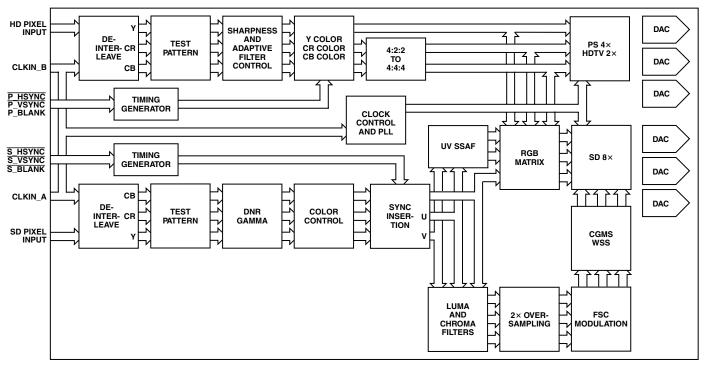

Figure 1-2 system diagram

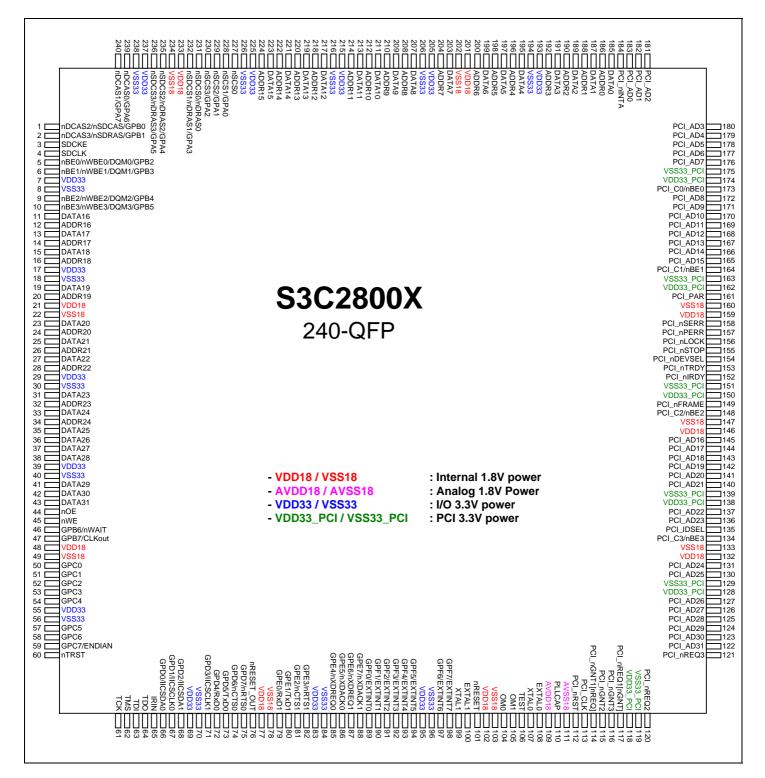

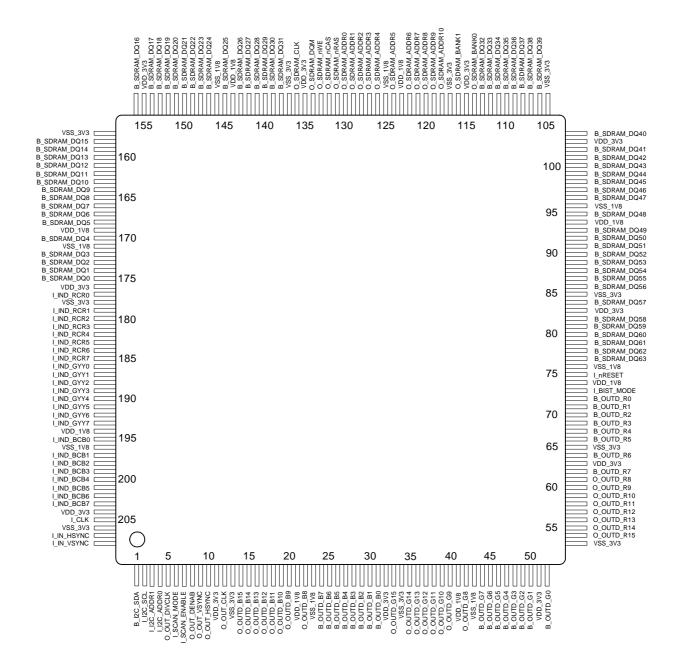

pin assignments for 352 FBGA

|    | 1               | 2           | 3                | 4              | 5               | 6           | 7      | 8           | 9           | 10          | 11              | 12     | 13          |

|----|-----------------|-------------|------------------|----------------|-----------------|-------------|--------|-------------|-------------|-------------|-----------------|--------|-------------|

| Α  | PVDDOP          | PVSSI       | MDATA7           | MDQM1          | MDATA3          | PVSSI       | PVDDOP | HOB7        | PVSSOP      | PVDDOP      | HOB0            | HOG6   | PVDDOP      |

| В  | MDQM2           | PVDDOP      | MDATA<br>10      | PVDDOP         | MDATA5          | PVSSOP      | PVDDI  | HO<br>VSYNC | HOB5        | новз        | HOB1            | FT24   | HOG3        |

| С  | MDATA<br>18     | MDATA<br>16 | MDATA<br>13      | MDATA<br>11    | MDATA9          | MDATA6      | MDATA1 | MDQM0       | HVID<br>CLK | HOB6        | HOB2            | FT135  | HOG4        |

| D  | MDATA<br>19     | MDATA<br>17 | MDATA<br>14      | MDATA<br>12    | PVDDI           | MDATA8      | MDATA4 | MDATA2      |             | HO<br>HSYNC | HOB4            | HOG7   | HOG5        |

| Е  | PVDDI           | PVSSI       | PVSSOP           | MDATA<br>15    |                 |             |        |             | I           | nonto       |                 | I      |             |

| F  | MDATA           | MDQM3       | MDATA            | MDATA          |                 |             |        |             |             |             |                 |        |             |

| G  | 25<br>MDATA     | MDATA       | 21<br>MDATA      | 20<br>MDATA    |                 |             | 3.3    | 1           |             |             |                 |        |             |

| н  | 26<br>MDATA     | 24<br>MDATA | 23<br>MDATA      | 22<br>PVSSOP   |                 |             | 5.5    | v           |             |             |                 |        |             |

| J  | 31<br>PVSSOP    | 28<br>MDATA | 27<br>PVSSOP     | MDATA          |                 |             | 1.8    | V           |             |             |                 |        |             |

| к  | nMCS1           | 30<br>nMWE  | nMCAS            | 29<br>nMRAS    |                 |             |        |             |             |             |                 |        |             |

| L  | МСКЕ            | nMCS0       | PVDDI            | PVSSI          |                 |             | 0V     |             |             |             |                 |        |             |

| М  | MBA1            | MBA0        | PVDDOP           | MCLK           |                 |             |        |             |             |             |                 |        |             |

| N  | MADDR<br>3      | MADDR<br>2  | MADDR<br>1       | MADDR<br>0     |                 |             |        |             |             |             |                 |        |             |

| Р  | PVDDOP          | ADDR<br>4   | MADDR<br>5       | MADDR<br>6     |                 |             |        |             |             |             |                 |        |             |

| R  | PVSSI           | PVDDI       | MADDR            | MADDR<br>8     |                 |             |        |             |             |             |                 |        |             |

| т  | MADDR<br>9      | PVDDOP      | 7<br>MADDR<br>10 | o<br>MDQM4     |                 |             |        |             |             |             |                 |        |             |

| U  | MDATA<br>32     | MDATA<br>33 | MDATA<br>34      | MDATA<br>35    |                 |             |        |             |             |             |                 |        |             |

| v  | PVSSOP          | PVDDOP      | MDATA<br>36      | MDATA<br>38    |                 |             |        |             |             |             |                 |        |             |

| w  | MDATA<br>37     | PVSSI       | PVDDI            |                |                 |             |        |             |             |             |                 |        |             |

| Y  | MDATA<br>39     | MDATA<br>40 | MDATA<br>42      | MDATA<br>43    |                 |             |        |             |             |             |                 |        |             |

| AA | MDQM5           | MDATA       | MDATA            | MDQM6          |                 |             |        |             |             |             |                 |        |             |

|    | MDATA           | 41<br>MDATA | 46<br>MDATA      | MDATA          |                 |             |        |             |             |             |                 |        |             |

| AB | 44              | 45          | 47<br>MDATA      | 50<br>MDATA    | MDATA           | MDATA       | DVCCOD | MDATA       | DD ATAO     | DD ATA 4    | DDATAO          | PDATA  | PDATA       |

| AC | PVDDOP<br>MDATA | PVSSI       | 51<br>MDATA      | 53<br>MDATA    | 55              | 56<br>MDATA | PVSSOP | 63          | PDATA2      | PDATA4      | PDATA9<br>PDATA | 13     | 14<br>PDATA |

| AD | 48<br>MDATA     | PVDDI       | 52               | 54             | PVDDOP<br>MDATA | 59<br>MDATA | PVSSI  | PDATA1      | PVDDOP      | PDATA8      | 10<br>PDATA     | PVSSOP | 15          |

| AE | 49              | PVSSOP      | PVSSI<br>MDATA   | PVDDI<br>MDATA | 60<br>MDATA     | 61          | PVDDI  | PDATA3      | PDATA7      | nPCBE1      | 11<br>PDATA     | PVSSI  | nPLOCK      |

| AF | PVDDOP          | MDQM7       | 57               | 58             | 62              | nPCBE0      | PDATA0 | PDATA5      | PDATA6      | PVDDOP      | 12              | PVDDI  | PVSSOP      |

SAMSUNG

ELECTRONICS

|    | 14         | 15             | 16             | 17             | 18             | 19             | 20          | 21          | 22          | 23             | 24             | 25           | 26            |

|----|------------|----------------|----------------|----------------|----------------|----------------|-------------|-------------|-------------|----------------|----------------|--------------|---------------|

| Α  | aRPR       | PAVSST<br>_HD1 | aHIRS          | aY             | PVSSOP         | PAVSST<br>_SD2 | aCVBS       | HOG1        | HOG5        | HOR1           | HOR2           | SI<br>VSYNC  | PVDDOP        |

| В  | aBPB       | PAVDDT<br>_HD1 | aGY            | PAVBB<br>_DAC  | PAVSST<br>_SD1 | aSCOM<br>P     | PVSSOP      | HOG0        | HOR4        | SICLK          | SI<br>HSYNC    | PVSSOP       | SIFLD         |

| С  | aHVREF     | PAVDDT<br>_HD2 | PAVDDI<br>_DAC | aSIRS          | PAVDDT<br>_SD2 | aC             | HOR7        | HOR3        | PVDDOP      | SIDATA6        | SIDATA3        | SIDATA2      | SIDATA0       |

| D  | aHCOM<br>P | PAVSST<br>_HD2 | PVSSI<br>_DAC  | PAVDDT<br>_SD1 | aSVREF         | HOG2           | HOR6        | HOR0        | SIDATA7     | SIDATA5        | SIDATA1        | SCANEN       | PVDDI         |

| Е  |            |                | _              |                |                |                |             |             |             | SIDATA4        | TSTON          | PVDDOP       | HIB7          |

| F  |            |                |                |                |                |                |             |             |             | PVSSI          | HI<br>HSYNC    | HI<br>VSYNC  | HIB3          |

| G  |            |                |                |                |                |                |             |             |             | HICLK          | HIB5           | HIB4         | HIB2          |

| н  |            |                |                |                |                |                |             |             |             | HIB6           | HIB1           | HIG7         | HIG5          |

| J  |            |                |                |                |                |                |             |             |             | PVDDOP         | HIB0           | HIG6         | HIG4          |

| к  |            |                |                |                |                |                |             |             |             | HIG3           | HIG2           | HIG1         | HIR7          |

| L  |            |                |                |                |                |                |             |             |             | HIG0           | PVDDI          | PVSSI        | PVDDOP        |

| М  |            |                |                |                |                |                |             |             |             | HIR6           | HIR5           | HIR4         | HIR3          |

| Ν  |            |                |                |                |                |                |             |             |             | HIR2           | HIR1           | HIR0         | PVDDI<br>_PLL |

| Ρ  |            |                |                |                |                |                |             |             |             | PAVDDT<br>_PLL | aPLL2          | aPLL1        | PVSSI<br>_PLL |

| R  |            |                |                |                |                |                |             |             |             | IBCLK          | PAVSST<br>_PLL | PAVBB<br>_PP | aPLL3         |

| т  |            |                |                |                |                |                |             |             |             | OLRCLK         | IPCM           | PVDDOP       | ILRCLK        |

| U  |            |                |                |                |                |                |             |             |             | OHDCL<br>K     | OSPDIF         | OBCLK        | ODCLK         |

| v  |            |                |                |                |                |                |             |             |             | PVDDI          | JTDI           | IVOH         | OADATA        |

| W  |            |                |                |                |                |                |             |             |             | PWM            | JTMS           | nJTRST       | JTDO          |

| Y  |            |                |                |                |                |                |             |             |             | TSCLK          | CLK27M         | nRESET       | JTCK          |

| AA |            |                |                |                |                |                |             |             |             | TSDATA<br>1    | TSDATA<br>7    | PVDDOP       | PVSSI         |

| AB |            | 1              | 1              | 1              |                |                |             |             |             | I2CCLK         | TSDATA<br>4    | TSVLD        | BEND          |

| AC | nPPERR     | nPISEL         | nPSTOP         | nPCBE2         |                | PDATA<br>23    | PVDDOP      | PDATA<br>28 | PDATA<br>31 | I2CDAT         | TSDATA<br>0    | TSDATA<br>3  | TSDATA<br>6   |

| AD | nPSERR     | nPGNT          | PVDDOP         | nPTRDY         | PDATA<br>17    | PDATA<br>18    | PDATA<br>22 | PVDDI       | PDATA<br>27 | PCISEL         | PVSSI          | PVDDI        | TSDATA<br>5   |

| AE | PVDDOP     | PCLK           | nPDSEL         | nPFRM          | PVSSI          | PDATA<br>16    | PDATA<br>21 | PDATA<br>24 | PVSSI       | PDATA<br>25    | PDATA<br>29    | PVSSOP       | TSDATA<br>2   |

| AF | nPINT      | nPRST          | nPREQ          | nPIRDY         | PVDDI          | PPAR           | PDATA<br>19 | PDATA<br>20 | nPCBE3      | PDATA<br>26    | PVSSOP         | PDATA<br>30  | PVDDOP        |

## **PIN DESCRIPTION**

| Pin<br>Name | Pin<br>Type | Pin Description                   | Circuit<br>Type | Pin<br>Number | Share<br>Pins |

|-------------|-------------|-----------------------------------|-----------------|---------------|---------------|

| nRESET      | I           | System Reset (Active Low)         |                 | Y25           | _             |

| CLK27M      | I           | SYSTEM Clock                      |                 | Y24           | _             |

| PWM         | 0           | PWM Output for clock recovery     |                 | W23           | _             |

| BEND        | I           | Big (High) or Little (Low) Endian |                 | AB26          | _             |

| OHDCLK      | 0           | HD clock output                   |                 | U23           | _             |

| IVOH        | I           | TEST PIN                          |                 | V25           | _             |

| TSTON       | I           | TEST PIN                          |                 | E24           | _             |

| SCAN_EN     | I           | TEST PIN                          |                 | D25           | _             |

| FT24        | I           | 24.576MHz Clock Input for TEST    |                 | B12           | _             |

| FT135       | I           | 135MHz Clock Input for TEST       |                 | C12           | _             |

| aPLL1       | AO          | PLL Loop Filter                   |                 | P25           | _             |

| aPLL2       | AO          | PLL Loop Filter                   |                 | P24           | _             |

| aPLL3       | AO          | PLL Loop Filter                   |                 | R26           | _             |

### Table 1-1. S5H2000X Pin Descriptions (System)

#### Table 1-1. S5H2000X Pin Descriptions (Continued: Debugger)

| Pin<br>Name | Pin<br>Type | Pin Description         | Circuit<br>Type | Pin<br>Number | Share<br>Pins |

|-------------|-------------|-------------------------|-----------------|---------------|---------------|

| JTDI        | I           | JTAG Input              |                 | V24           | -             |

| JTDO        | 0           | JTAG Output             |                 | W26           | -             |

| JTCK        | I           | JTAG Clock              |                 | Y26           | -             |

| nJTRST      | I           | JTAG Reset (Active Low) |                 | W25           | -             |

| JTMS        | I           | JTAG Mode Select        |                 | W24           | _             |

## Table 1-1. S5H2000X Pin Descriptions (Continued: I2C)

| Pin<br>Name | Pin<br>Type | Pin Description  | Circuit<br>Type | Pin<br>Number | Share<br>Pins |

|-------------|-------------|------------------|-----------------|---------------|---------------|

| I2CCLK      | 0           | I2C Clock Output |                 | AB23          | _             |

| I2CDATA     | I/O         | I2C DATA         |                 | AC23          | _             |

| Pin<br>Name           | Pin<br>Type | Pin Description                      | Circuit<br>Type | Pin<br>Number | Share<br>Pins |

|-----------------------|-------------|--------------------------------------|-----------------|---------------|---------------|

|                       |             |                                      |                 | AC22          |               |

|                       |             |                                      |                 | AF25          |               |

| PDATA31               |             |                                      |                 | AE24          |               |

| ~                     | I/O         | 32bit PCI Data and Address (33MHz)   |                 | AC21          |               |

| PDATA24               | ., 0        |                                      |                 | AD22          |               |

|                       |             |                                      |                 | AF23          |               |

|                       |             |                                      |                 | AE23          |               |

|                       |             |                                      |                 | AE21          |               |

|                       |             |                                      |                 | AC19          |               |

|                       |             |                                      |                 | AD20          |               |

| PDATA23               |             |                                      |                 | AE20          |               |

|                       | I/O         | 32bit PCI Data and Address (33MHz)   |                 | AF21          |               |

| PDATA16               | 1/0         | Szbit i Or Data and Address (SSWITZ) |                 | AF20          |               |

|                       |             |                                      |                 | AD19          |               |

|                       |             |                                      |                 | AD18          |               |

|                       |             |                                      |                 | AE19          | _             |

|                       |             |                                      |                 | AD13          |               |

|                       |             |                                      |                 | AC13          |               |

| PDATA15               |             |                                      |                 | AC12          |               |

|                       | I/O         | 32bit PCI Data and Address (33MHz)   |                 | AF11          |               |

| PDATA8                | 1,0         |                                      |                 | AE11          |               |

|                       |             |                                      |                 | AD11          |               |

|                       |             |                                      |                 | AC11          |               |

|                       |             |                                      |                 | AD10          |               |

|                       |             |                                      |                 | AE9           |               |

|                       |             |                                      |                 | AF9           |               |

| PDATA7                |             |                                      |                 | AF8           |               |

| PDATA7<br>~<br>PDATA0 | I/O         | 32bit PCI Data and Address (33MHz)   |                 | AC10          |               |

|                       |             |                                      |                 | AE8           |               |

|                       |             |                                      |                 | AC9           |               |

|                       |             |                                      |                 | AD8           |               |

|                       |             |                                      |                 | AF7           |               |

Table 1-1. S5H2000X Pin Descriptions (Continued: PCI)

| Pin<br>Name | Pin<br>Type | Pin Description                               | Circuit<br>Type | Pin<br>Number | Share<br>Pins |

|-------------|-------------|-----------------------------------------------|-----------------|---------------|---------------|

|             |             |                                               |                 | AF22          |               |

| nPCBE3      | 1/0         | this DCI Due Command and Dute English         |                 | AC17          |               |

| ~<br>nPCBE0 | I/O         | 4bit PCI Bus Commend and Byte Enable          |                 | AE10          | -             |

|             |             |                                               |                 | AF6           |               |

| PPAR        | I/O         | PCI parity                                    |                 | AF19          |               |

| nPFRM       | I/O         | PCI cycle frame (Active LOW)                  |                 | AE17          |               |

| nPTRDY      | I/O         | PCI target ready (Active LOW)                 |                 | AD17          |               |

| nPIRDY      | I/O         | PCI initiator ready (Active LOW)              |                 | AF17          |               |

| nPSTOP      | I/O         | PCI stop (Active LOW)                         |                 | AC16          |               |

| nPDSEL      | I/O         | PCI device select (Active LOW)                |                 | AE16          |               |

| nPREQ       | 0           | PCI Bus request (Active LOW)                  |                 | AF16          |               |

| nPISEL      | I           | PCI initialization device select (Active LOW) |                 | AC15          |               |

| nPGNT       | I           | PCI Bus grant (Active LOW)                    |                 | AD15          |               |

| PCLK        | I           | PCI clock                                     |                 | AE15          |               |

| nPRST       | I           | PCI reset (Active LOW)                        |                 | AF15          |               |

| nPPERR      | I/O         | PCI parity error (Active LOW)                 |                 | AC14          |               |

| nPSERR      | 0           | PCI system error (Active LOW)                 |                 | AD14          |               |

| nPINT       | 0           | PCI interrupt signal (Active LOW)             |                 | AF14          |               |

| nPLOCK      | I/O         | PCI lock signal (Active LOW)                  |                 | AE13          |               |

| PCISEL      | I           | PCI operation voltage selection (fixed 0V)    |                 | AD23          |               |

Table 1-1. S5H2000X Pin Descriptions (Continued: PCI)

## Table 1-1. S5H2000X Pin Descriptions (Continued: TS DEMUX)

| Pin<br>Name  | Pin<br>Type                       | Pin Description                   | Circuit<br>Type | Pin<br>Number | Share<br>Pins |

|--------------|-----------------------------------|-----------------------------------|-----------------|---------------|---------------|

|              |                                   |                                   |                 | AA24          |               |

|              |                                   |                                   |                 | AC26          |               |

|              |                                   |                                   |                 | AD26          |               |

| TSDATA7      | Ohit Transport Stream DoMuy Input |                                   | AB24            |               |               |

| ~<br>TSDATA0 | I                                 | 8bit Transport Stream DeMux Input |                 | AC25          |               |

| ISDATA       |                                   |                                   |                 | AE26          |               |

|              |                                   |                                   |                 | AA23          |               |

|              |                                   |                                   |                 | AC24          |               |

| TSCLK        | I                                 | Transport Stream DeMux Clock      |                 | Y23           |               |

#### PRODUCT OVERVIEW

| TSVLD        | I           | Transport Stream DeMux Valid                   |                 | AB25          |               |

|--------------|-------------|------------------------------------------------|-----------------|---------------|---------------|

|              | Tab         | e 1-1. S5H2000X Pin Descriptions (Continued: S | DRAM)           |               |               |

| Pin<br>Name  | Pin<br>Type | Pin Description                                | Circuit<br>Type | Pin<br>Number | Share<br>Pins |

|              |             |                                                |                 | AC8           |               |

|              |             |                                                |                 | AF5           |               |

|              |             |                                                |                 | AE6           |               |

| MDATA63      | I/O         | 64bit SDRAM Data                               |                 | AE5           |               |

| ~<br>MDATA56 | ., 0        |                                                |                 | AD6           |               |

|              |             |                                                |                 | AF4           |               |

|              |             |                                                |                 | AF3           |               |

|              |             |                                                |                 | AC6           |               |

|              |             |                                                |                 | AC5           |               |

|              |             |                                                |                 | AD4           |               |

|              |             |                                                |                 | AC4           |               |

| MDATA55<br>~ | I/O         | 64bit SDRAM Data                               |                 | AD3           |               |

| MDATA48      |             |                                                |                 | AC3           |               |

|              |             |                                                |                 | AB4           |               |

|              |             |                                                |                 | AE1           |               |

|              |             |                                                |                 | AD1           |               |

|              |             |                                                |                 | AB3           |               |

|              |             |                                                |                 | AA3           |               |

| MDATA47      |             |                                                |                 | AB2           |               |

| ~            | I/O         | 64bit SDRAM Data                               |                 | AB1           |               |

| MDATA40      |             |                                                |                 | Y4            |               |

|              |             |                                                |                 | Y3            |               |

|              |             |                                                |                 | AA2           |               |

|              |             |                                                |                 | Y2            |               |

|              |             |                                                |                 | Y1            |               |

|              |             |                                                |                 | V4            |               |

| MDATA39      |             |                                                |                 | W1            |               |

| ~            | I/O         | 64bit SDRAM Data                               |                 | V3            |               |

| MDATA32      |             |                                                |                 | U4            |               |

|              |             |                                                |                 | U3            |               |

|              |             |                                                |                 | U2            |               |

|              |             |                                                |                 | U1            |               |

| Pin<br>Name              | Pin<br>Type | Pin Description  | Circuit<br>Type | Pin<br>Number | Share<br>Pins |

|--------------------------|-------------|------------------|-----------------|---------------|---------------|

|                          |             |                  |                 | H1            |               |

|                          |             |                  |                 | J2            |               |

|                          |             |                  |                 | J4            |               |

| MDATA31                  | I/O         | 64bit SDRAM Data |                 | H2            |               |

| ~<br>MDATA24             | 1/0         |                  |                 | H3            |               |

|                          |             |                  |                 | G1            |               |

|                          |             |                  |                 | F1            |               |

|                          |             |                  |                 | G2            |               |

|                          |             |                  |                 | G3            |               |

|                          |             |                  |                 | G4            |               |

|                          |             |                  |                 | F3            |               |

| MDATA23                  | I/O         | 64bit SDRAM Data |                 | F4            |               |

| ~<br>MDATA16             | 1/0         |                  |                 | D1            |               |

|                          |             |                  |                 | C1            |               |

|                          |             |                  |                 | D2            |               |

|                          |             |                  |                 | C2            |               |

|                          |             |                  |                 | E4            |               |

|                          |             |                  |                 | D3            |               |

|                          |             |                  |                 | C3            |               |

| MDATA16                  | I/O         | 64bit SDRAM Data |                 | D4            |               |

| ~<br>MDATA8              | 1/0         |                  |                 | C4            |               |

|                          |             |                  |                 | B3            |               |

|                          |             |                  |                 | C5            |               |

|                          |             |                  |                 | D6            |               |

|                          |             |                  |                 | A3            |               |

|                          |             |                  |                 | C6            |               |

|                          |             |                  |                 | B5            |               |

| MDATA7<br>~ I/<br>MDATA0 | I/O         | 64bit SDRAM Data |                 | D7            |               |

|                          | "0          |                  |                 | A5            |               |

|                          |             |                  |                 | D8            |               |

|                          |             |                  |                 | C7            |               |

|                          |             |                  |                 | D9            |               |

Table 1-1. S5H2000X Pin Descriptions (Continued: SDRAM)

| Pin<br>Name | Pin<br>Type | Pin Description                   | Circuit<br>Type | Pin<br>Number | Share<br>Pins |   |   |   |   |                        |  |    |  |

|-------------|-------------|-----------------------------------|-----------------|---------------|---------------|---|---|---|---|------------------------|--|----|--|

|             |             |                                   |                 | Т3            |               |   |   |   |   |                        |  |    |  |

|             |             |                                   |                 | T1            |               |   |   |   |   |                        |  |    |  |

|             |             |                                   |                 | R4            |               |   |   |   |   |                        |  |    |  |

|             |             |                                   |                 | R3            |               |   |   |   |   |                        |  |    |  |

| MADDR10     |             |                                   |                 | P4            |               |   |   |   |   |                        |  |    |  |

| ~           | 0           | 11bit SDRAM Address               |                 | P3            |               |   |   |   |   |                        |  |    |  |

| MADDR0      |             |                                   |                 | P2            |               |   |   |   |   |                        |  |    |  |

|             |             |                                   |                 | N1            |               |   |   |   |   |                        |  |    |  |

|             |             |                                   |                 | N2            |               |   |   |   |   |                        |  |    |  |

|             |             |                                   |                 | N3            |               |   |   |   |   |                        |  |    |  |

|             |             |                                   |                 | N4            |               |   |   |   |   |                        |  |    |  |

|             |             |                                   |                 | AF2           |               |   |   |   |   |                        |  |    |  |

|             |             |                                   | AA4             |               |               |   |   |   |   |                        |  |    |  |

| MDQM7       |             |                                   |                 | AA1           |               |   |   |   |   |                        |  |    |  |

|             | 0           | 8bit SDRAM Data MASK              |                 | T4            |               |   |   |   |   |                        |  |    |  |

| ~<br>MDQM0  | 0           | 0                                 | 0               | 0             | 0             | 0 | 0 | 0 | 0 | ODIT ODITANI Data MASK |  | F2 |  |

| MDQMO       |             |                                   |                 | B1            |               |   |   |   |   |                        |  |    |  |

|             |             |                                   |                 | A4            |               |   |   |   |   |                        |  |    |  |

|             |             |                                   |                 | C8            |               |   |   |   |   |                        |  |    |  |

| MBA1        | 0           | 2bit SDRAM Bank Address           |                 | M1            |               |   |   |   |   |                        |  |    |  |

| MBA0        | U           |                                   |                 | M2            |               |   |   |   |   |                        |  |    |  |

| MCLK        | 0           | SDRAM Clock                       |                 | M4            |               |   |   |   |   |                        |  |    |  |

| MCKE        | 0           | SDRAM Clock Enable                |                 | L1            |               |   |   |   |   |                        |  |    |  |

| nMCS1       | 0           | SDRAM Chip Select 1 (Active LOW)  |                 | K1            |               |   |   |   |   |                        |  |    |  |

| nMCS0       | 0           | SDRAM Chip Select 0 (Active LOW)  |                 | L2            |               |   |   |   |   |                        |  |    |  |

| nMWE        | 0           | SDRAM Write Enable (Active LOW)   |                 | K2            |               |   |   |   |   |                        |  |    |  |

| nMRAS       | 0           | SDRAM Row Address (Active LOW)    |                 | K4            |               |   |   |   |   |                        |  |    |  |

| nMCAS       | 0           | SDRAM Column Address (Active LOW) |                 | K3            |               |   |   |   |   |                        |  |    |  |

## Table 1-1. S5H2000X Pin Descriptions (Continued: SDRAM)

| Pin<br>Type | Pin Description          | Circuit<br>Type                                                                        | Pin<br>Number                                                                                                  | Share<br>Pins                                                                                                                       |

|-------------|--------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|             |                          |                                                                                        | D22                                                                                                            |                                                                                                                                     |

|             | 8bit SD Video Data Input |                                                                                        | C23                                                                                                            |                                                                                                                                     |

|             |                          |                                                                                        | D23                                                                                                            |                                                                                                                                     |

| 1           |                          |                                                                                        | E23                                                                                                            |                                                                                                                                     |

| I           |                          |                                                                                        | C24                                                                                                            |                                                                                                                                     |

|             |                          |                                                                                        | C25                                                                                                            |                                                                                                                                     |

|             |                          |                                                                                        | D24                                                                                                            |                                                                                                                                     |

|             |                          |                                                                                        | C26                                                                                                            |                                                                                                                                     |

| I           | SD Video Data Clock      |                                                                                        | B23                                                                                                            |                                                                                                                                     |

| I           | SD Video H Sync          |                                                                                        | B24                                                                                                            |                                                                                                                                     |

| I           | SD Video V Sync          |                                                                                        | A25                                                                                                            |                                                                                                                                     |

| I           | SD Video Field ID        |                                                                                        | B26                                                                                                            |                                                                                                                                     |

|             |                          | TypeI8bit SD Video Data InputI8bit SD Video Data ClockISD Video H SyncISD Video V Sync | TypeTypeI8bit SD Video Data InputI8bit SD Video Data ClockISD Video Data ClockISD Video H SyncISD Video V Sync | TypeTypeNumberID22C23D23D23Bbit SD Video Data InputE23C24C24C25D24D24C26ISD Video Data ClockIISD Video H SyncB23ISD Video V SyncA25 |

Table 1-1. S5H2000X Pin Descriptions (Continued: External Video data input-SD)

## Table 1-1. S5H2000X Pin Descriptions (Continued: External Video data input-HD)

| Pin<br>Name | Pin<br>Type | Pin Description              | Circuit<br>Type | Pin<br>Number | Share<br>Pins |

|-------------|-------------|------------------------------|-----------------|---------------|---------------|

|             |             |                              |                 | K26           |               |

|             |             |                              |                 | M23           |               |

| HIR7        |             |                              |                 | M24           |               |

| ~           | I           | HD Video <b>R</b> Data Input |                 | M25           |               |

| ~<br>HIR0   | I           |                              |                 | M26           |               |

|             |             |                              |                 | N23           |               |

|             |             |                              |                 | N24           |               |

|             |             |                              |                 | N25           |               |

|             |             |                              |                 | H25           |               |

|             |             |                              |                 | J25           |               |

| HIG7        |             |                              |                 | H26           |               |

|             | I           | HD Video C Data Input        |                 | J26           |               |

| ~<br>HIG0   | 1           | HD Video <b>G</b> Data Input |                 | K23           |               |

|             |             |                              |                 | K24           |               |

|             |             |                              |                 | K25           |               |

|             |             |                              |                 | L23           |               |

| Pin<br>Name | Pin<br>Type | Pin Description              | Circuit<br>Type | Pin<br>Number | Share<br>Pins |

|-------------|-------------|------------------------------|-----------------|---------------|---------------|

|             |             |                              |                 | E26           |               |

|             |             |                              |                 | H23           |               |

| HIB7        |             |                              |                 | G24           |               |

|             | 1           | HD Video <b>B</b> Data Input |                 | G25           |               |

| ~<br>HIB0   | 1           |                              |                 | F26           |               |

|             |             |                              |                 | G26           |               |

|             |             |                              |                 | H24           |               |

|             |             |                              |                 | J24           |               |

| HICLK       | I           | HD Video Data Clock          |                 | G23           |               |

| HIHSYNC     | I           | HD Video H Sync              |                 | F24           |               |

| HIVSYNC     | I           | HD Video V Sync              |                 | F25           |               |

## Table 1-1. S5H2000X Pin Descriptions (Continued: External Video data input-HD)

#### Table 1-1. S5H2000X Pin Descriptions (Continued: Video data output-analog SD)

| Pin<br>Name | Pin<br>Type | Pin Description                  | Circuit<br>Type | Pin<br>Number | Share<br>Pins |

|-------------|-------------|----------------------------------|-----------------|---------------|---------------|

| aCVBS       | AO          | SD Analog Composite Video Output |                 | A20           |               |

| aY          | AO          | SD Analog Luminance Video Output |                 | A17           |               |

| aC          | AO          | SD Analog Chroma Video Output    |                 | C19           |               |

| aSCOMP      | AO          | SD DAC Compensation              |                 | B19           |               |

| aSVREF      | AO          | SD DAC Voltage Reference         |                 | D18           |               |

| aSIRS       | AO          | SD DAC Current Reference         |                 | C17           |               |

#### Table 1-1. S5H2000X Pin Descriptions (Continued: Video data output-analog HD)

| Pin<br>Name | Pin<br>Type | Pin Description          | Circuit<br>Type | Pin<br>Number | Share<br>Pins |

|-------------|-------------|--------------------------|-----------------|---------------|---------------|

| aRPR        | AO          | HD Analog Video R Output |                 | A14           |               |

| aGY         | AO          | HD Analog Video G Output |                 | B16           |               |

| aBPB        | AO          | HD Analog Video B Output |                 | B14           |               |

| aHCOMP      | AO          | HD DAC Compensation      |                 | D14           |               |

| aHVREF      | AO          | HD DAC Voltage Reference |                 | C14           |               |

| aHIRS       | AO          | HD DAC Current Reference |                 | A16           |               |

| Pin<br>Name | Pin<br>Type | Pin Description               | Circuit<br>Type | Pin<br>Number | Share<br>Pins |

|-------------|-------------|-------------------------------|-----------------|---------------|---------------|

|             |             |                               |                 | C20           |               |

|             |             |                               |                 | D20           |               |

| HOR7        |             |                               |                 | A22           |               |

| ~           | 0           | HD Video <b>R</b> Data Output |                 | B22           |               |

| HOR0        | 0           |                               |                 | C21           |               |

|             |             |                               |                 | A23           |               |

|             |             |                               |                 | A24           |               |

|             |             |                               |                 | D21           |               |

|             |             |                               |                 | D12           |               |

|             |             |                               |                 | A12           |               |

| HOG7        |             | O HD Video G Data Output      |                 | D13           |               |

| ~           | 0           |                               |                 | C13           |               |

| HOG0        | 0           |                               |                 | B13           |               |

| 11000       |             |                               |                 | D19           |               |

|             |             |                               |                 | A21           |               |

|             |             |                               |                 | B21           |               |

|             |             |                               |                 | A8            |               |

|             |             |                               |                 | C10           |               |

| HOB7        |             |                               |                 | B9            |               |

| ~           | 0           | HD Video <b>B</b> Data Output |                 | D11           |               |

| HOB0        | 0           |                               |                 | B10           |               |

|             |             |                               |                 | C11           |               |

|             |             |                               |                 | B11           |               |

|             |             |                               |                 | A11           |               |

| HVIDCLK     | Ι           | HD Video Data Clock           |                 | C9            |               |

| HOVSYNC     | 0           | HD Video H Sync Output        |                 | B8            |               |

| HOHSYNC     | 0           | HD Video V Sync Output        |                 | D10           |               |

# Table 1-1. S5H2000X Pin Descriptions (Continued: External Video data output-digital HD)

| Pin<br>Name | Pin<br>Type | Pin Description                    | Circuit<br>Type | Pin<br>Number | Share<br>Pins |

|-------------|-------------|------------------------------------|-----------------|---------------|---------------|

| ILRCLK      | I           | Audio Left/Right Clock Input       |                 | T26           |               |

| IBCLK       | I           | Bit Clock Input                    |                 | R23           |               |

| IPCM        | I           | PCM Data Input                     |                 | T24           |               |

| OBCLK       | 0           | Bit Clock Output                   |                 | U25           |               |

| ODCLK       | 0           | DAC Clock Output                   |                 | U26           |               |

| OLRCLK      | 0           | Left/Right indicate signal         |                 | T23           |               |

| OADATA      | 0           | DATA Output for External audio DAC |                 | V26           |               |

| OSPDIF      | 0           | SPDIF Output                       |                 | U24           |               |

#### Table 1-1. S5H2000X Pin Descriptions (Continued: Audio output)

| Pin<br>Name | Pin<br>Type | Pin Description          | Circuit<br>Type | Pin<br>Number | Share<br>Pins |

|-------------|-------------|--------------------------|-----------------|---------------|---------------|

|             |             |                          |                 | A1            |               |

|             |             |                          |                 | A7            |               |

|             |             |                          |                 | A10           |               |

|             |             |                          |                 | A13           |               |

|             |             |                          |                 | A26           |               |

|             |             |                          |                 | B2<br>B4      |               |

|             |             |                          |                 | Б4<br>C22     |               |

|             |             |                          |                 | E25           |               |

|             |             |                          |                 | J23           |               |

|             |             |                          |                 | L26           |               |

|             |             |                          |                 | M3            |               |

|             |             |                          |                 | P1            |               |

| PVDDOP      |             | Digital PAD Power (3.3V) |                 | T2            |               |

| _           |             |                          |                 | T25           | _             |

|             |             |                          |                 | V2            |               |

|             |             |                          |                 | W4            |               |

|             |             |                          |                 | AA25          |               |

|             |             |                          |                 | AC1           |               |

|             |             |                          |                 | AC18          |               |

|             |             |                          |                 | AC20          |               |

|             |             |                          |                 | AD5           |               |

|             |             |                          |                 | AD9           |               |

|             |             |                          |                 | AD16          |               |

|             |             |                          |                 | AE14          |               |

|             |             |                          |                 | AF1           |               |

|             |             |                          |                 | AF10<br>AF26  |               |

|             |             |                          |                 | AF26<br>A9    |               |

|             |             |                          |                 | A18           |               |

|             |             |                          |                 | B6            |               |

|             |             |                          |                 | B20           |               |

|             |             |                          |                 | B25           |               |

| PVSSOP      |             | Digital PAD Ground       |                 | E3            |               |

|             |             |                          |                 | H4            | -             |

|             |             |                          |                 | J1            |               |

|             |             |                          |                 | J3            |               |

|             |             |                          |                 | V1            |               |

|             |             |                          |                 | AC7           |               |

|             |             |                          |                 | AD12          |               |

Table 1-1. S5H2000X Pin Descriptions (Continued: Power)

| Pin<br>Name | Pin<br>Type | Pin Description               | Circuit<br>Type | Pin<br>Number | Share<br>Pins |

|-------------|-------------|-------------------------------|-----------------|---------------|---------------|

|             |             |                               |                 | AE2           |               |

|             |             |                               |                 | AE25          |               |

|             |             |                               |                 | AF13          |               |

|             |             |                               |                 | AF24          |               |

|             |             |                               |                 | B7            |               |

|             |             |                               |                 | D5            |               |

|             |             |                               |                 | D26           |               |

|             |             |                               |                 | E1            |               |

|             |             |                               |                 | L3            |               |

| PVDDI       | _           | Digital Internal Power (1.8V) |                 | L24           | _             |

|             |             |                               |                 | R2            |               |

|             |             |                               |                 | V23           |               |

|             |             |                               |                 | W3            |               |

|             |             |                               |                 | AD2           |               |

|             |             |                               |                 | AD21          |               |

|             |             |                               |                 | AD25<br>AE4   |               |

|             |             |                               |                 | AE4<br>AE7    |               |

|             |             |                               |                 | AF12          |               |

|             |             |                               |                 | AF18          |               |

|             |             |                               |                 | A2            |               |

|             |             |                               |                 | A6            |               |

|             |             |                               |                 | E2            |               |

|             |             |                               |                 | F23           |               |

|             |             |                               |                 | L4            |               |

|             |             |                               |                 | L25           |               |

|             |             |                               |                 | R1            |               |

| PVSSI       |             | Digital Internal Ground       |                 | W2            |               |

|             | _           | 0                             |                 | AA26          | _             |

|             |             |                               |                 | AC2           |               |

|             |             |                               |                 | AD7           |               |

|             |             |                               |                 | AD24          |               |

|             |             |                               |                 | AE3           |               |

|             |             |                               |                 | AE12          |               |

|             |             |                               |                 | AE18          |               |

|             |             |                               |                 | AE22          |               |

Table 1-1. S5H2000X Pin Descriptions (Continued: Power)

| Pin<br>Name              | Pin<br>Type | Pin Description                                  | Circuit<br>Type | Pin<br>Number | Share<br>Pins |

|--------------------------|-------------|--------------------------------------------------|-----------------|---------------|---------------|

|                          |             |                                                  |                 | A2            |               |

|                          |             |                                                  |                 | A6            |               |

|                          |             |                                                  |                 | E2            |               |

|                          |             |                                                  |                 | F23           |               |

|                          |             |                                                  |                 | L4            |               |

|                          |             |                                                  |                 | L25           |               |

|                          |             |                                                  |                 | R1            |               |

| PVSSI                    | _           | Digital Internal Ground                          |                 | W2            |               |

|                          |             |                                                  |                 | AA26          |               |

|                          |             |                                                  |                 | AC2           |               |

|                          |             |                                                  |                 | AD7           |               |

|                          |             |                                                  |                 | AD24          |               |

|                          |             |                                                  |                 | AE3           |               |

|                          |             |                                                  |                 | AE12          |               |

|                          |             |                                                  |                 | AE18          |               |

|                          |             |                                                  |                 | AE22          |               |

|                          | -           | DAC PAD Power (3.3V)                             |                 | B15           |               |

| PAVDDT                   |             |                                                  |                 | C15           | _             |

|                          |             |                                                  |                 | C18           |               |

|                          |             |                                                  |                 | D17           |               |

|                          | -           |                                                  |                 | A15           |               |

| PAVSST                   |             | DAC PAD Ground                                   |                 | A19           | _             |

|                          |             |                                                  |                 | B18           |               |

| PVDDI_DAC                |             | DAC Internel Dewer (2.2)/)                       |                 | D15<br>C16    |               |

| PVDDI_DAC                | -           | DAC Internal Power (3.3V)<br>DAC Internal Ground |                 | D16           | _             |

| PAVBB_DAC                | _           | DAC Internal Ground<br>DAC Bulk Ground           |                 | B17           | -             |

| PAVBB_DAC                | _           |                                                  |                 | P23           | _             |

| PAVDDT_PLL<br>PAVSST_PLL | _           | PLL PAD Power (1.8V) PLL PAD Ground              |                 | P23<br>R24    |               |

| PAVSST_PLL<br>PAVBB_PLL  |             | PLL PAD Ground<br>PLL Bulk Ground                |                 | R24<br>R25    | -             |

| PAVBB_PLL<br>PVDDI_PLL   | -           | PLL Bulk Ground<br>PLL Internal Power (1.8V)     |                 | R25<br>N26    | -             |

| PVSSI_PLL                | -           | PLL Internal Ground                              |                 | P26           | _             |

Table 1-1. S5H2000X Pin Descriptions (Continued: Power)

NOTES

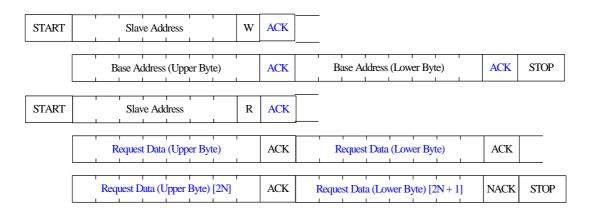

# **2** ADDRESS SPACE

## OVERVIEW

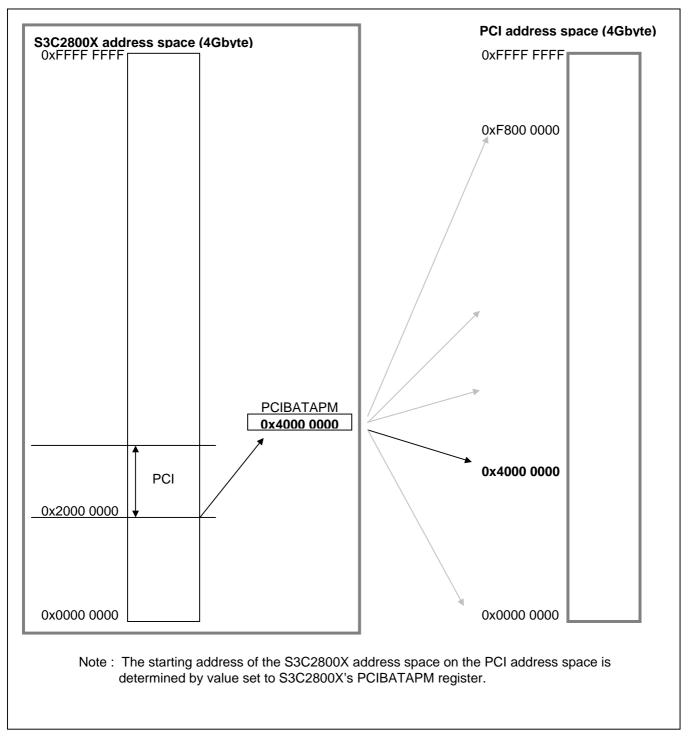

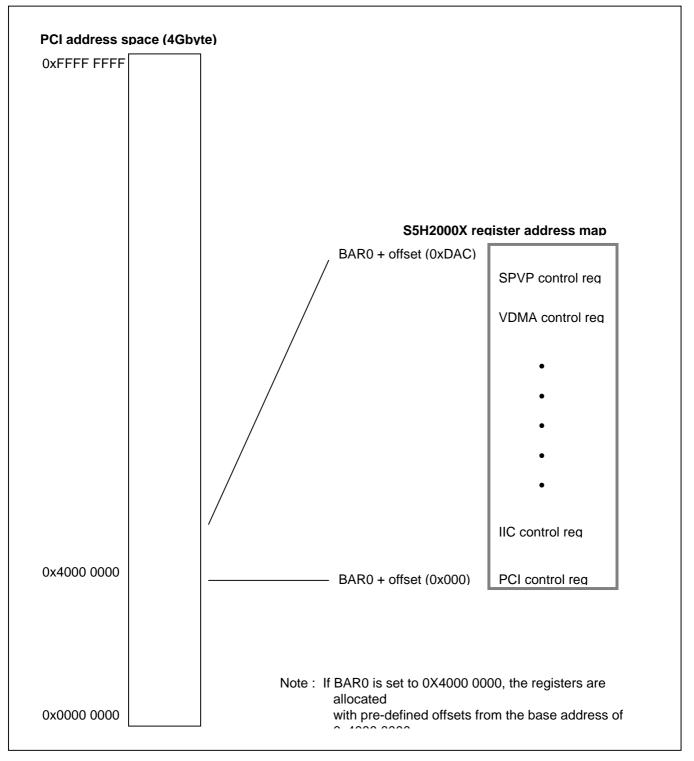

Basically, S5H2000X communicates with external devices through PCI.

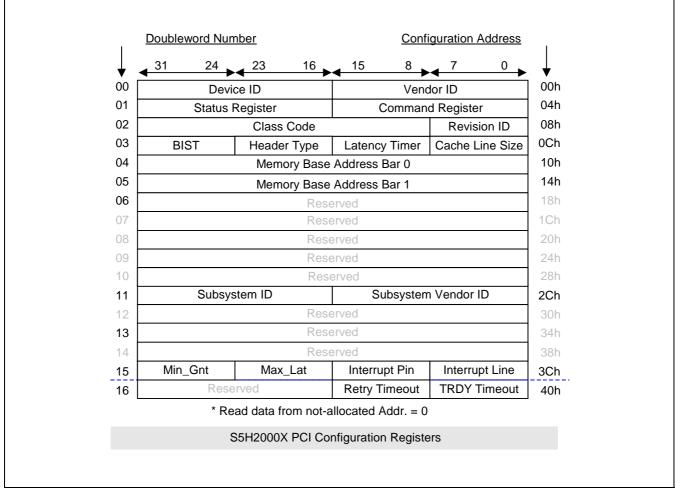

S5H2000X requests the required amount of memory (The amount should be previously indicated.) From the host through the base address registers, BAR0 and BAR1, of the PCI configuration registers. All the registers of the S5H2000X have addresses which are determined by offset from BAR0 and BAR1. The address space that the PCI host device allocates to S5H2000X BAR0 and BAR1 exists within the range of the PCI address space (32 bits – 4GB (Giga bytes).

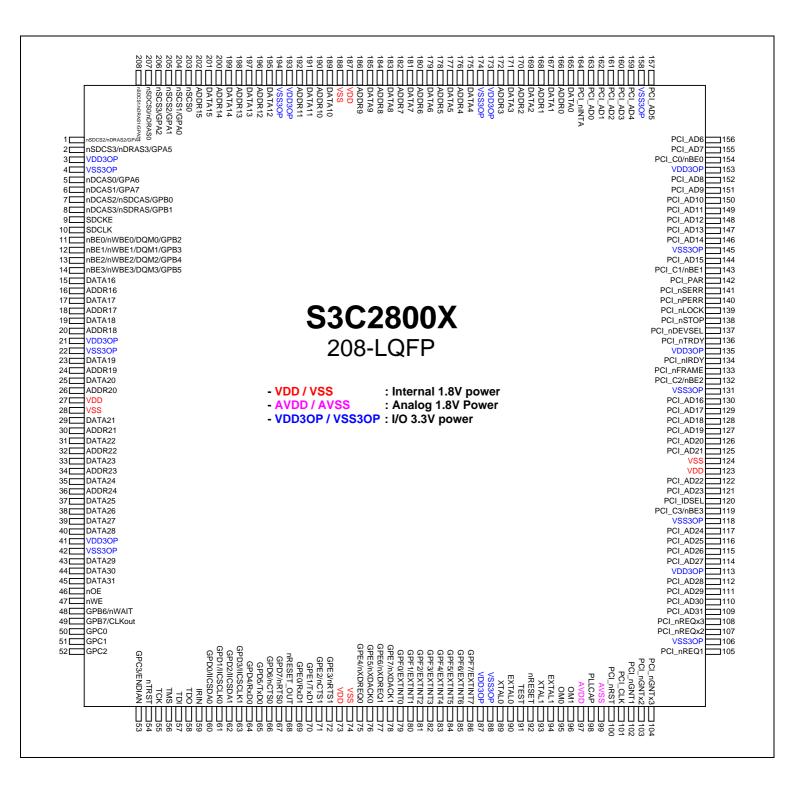

For example, if the S3C2800X is the PCI host device, it detects S5H2000X during PCI scanning upon boot-up and recognizes the requested address space (memory or I/O size) via BAR0and BAR1. S3C2800X is designed to have a maximum PCI address space of 128MB (Mega bytes).

Hence, although the total PCI address space is 4GB because the PCI address bus is 32 bits, the S3C2800X can only use up to 128MB of address space. The S3C2800X has a built-in address conversion logic gate which picks up the desired starting address from the PCI address space of 4GB.

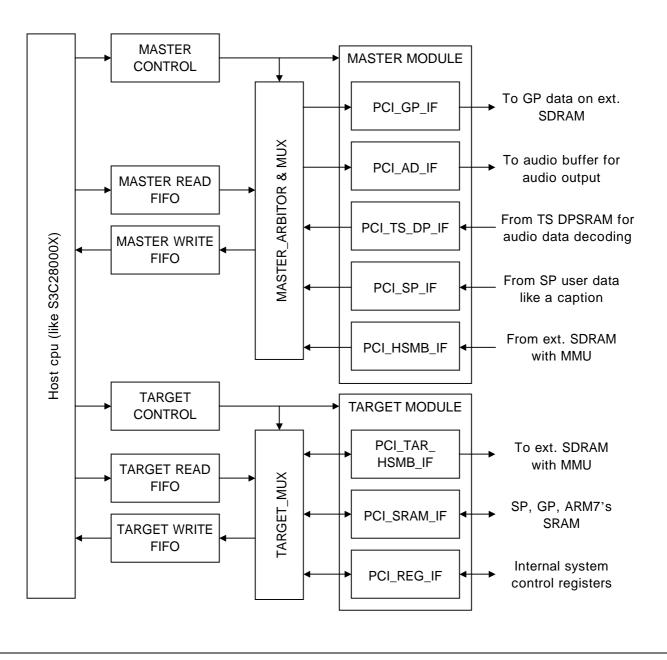

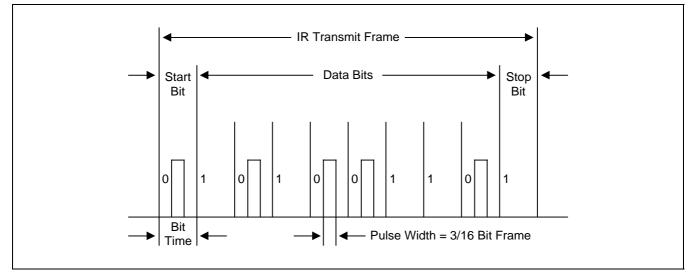

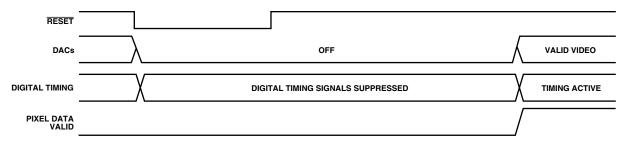

The following example describes in detail the addressing for a device constructed with S5H2000X and S3C2800X.